Product Summary

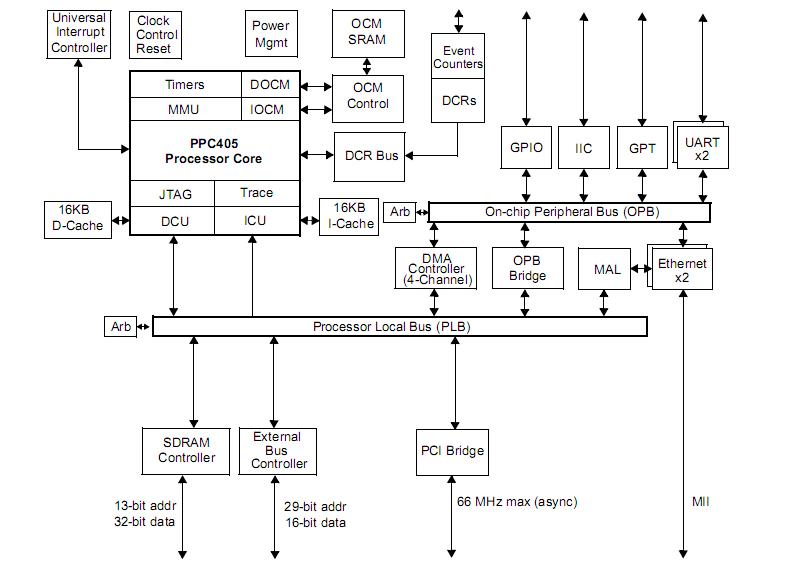

The PPC405EP-3LB266C is a PowerPC 405EP Embedded Processor. Designed specifically to address embedded applications, the PPC405EP-3LB266C provides a high-performance, low-power solution that interfaces to a wide range of peripherals by incorporating on-chip power management features and lower power dissipation requirements. The PPC405EP-3LB266C contains a high-performance RISC processor core, SDRAM controller, PCI bus interface, Ethernet interface, control for external ROM and peripherals, DMA with scatter-gather support, serial ports, IIC interface, and general purpose I/O.

Parametrics

PPC405EP-3LB266C absolute maximum ratings: (1)Supply Voltage (Internal Logic):0 to +1.95V; (2)Supply Voltage (I/O Interface):0 to +3.6V; (3)PLL Supply Voltage:0 to +1.95V; (4)Input Voltage (1.8V CMOS receivers):0 to +1.95V; (5)Input Voltage (3.3V LVTTL receivers):0 to +3.6V; (6)Input Voltage (5.0V LVTTL receivers):0 to +5.5V; (7)Storage Temperature Range:-55℃ to +150℃; (8)Case temperature under bias:-40℃ to +120℃.

Features

PPC405EP-3LB266C features: (1)AMCC PowerPC 405 32-bit RISC processor core operating up to 333MHz with 16KB Dand I-caches; (2)PC-133 synchronous DRAM (SDRAM) interface: 32-bit interface for non-ECC applications; (3)4KB on-chip memory (OCM); (4)External peripheral bus: Flash ROM/Boot ROM interface; Direct support for 8- or 16-bit SRAM and external peripherals; Up to five devices; (5)DMA support for memory and UARTs.: Scatter-gather chaining supported; Four channels; (6)PCI Revision 2.2 compliant interface (32-bit, up to 66MHz): Asynchronous PCI Bus interface; Internal or external PCI Bus Arbiter; (7)Two Ethernet 10/100Mbps (full-duplex) ports with media independent interface (MII); (8)Programmable interrupt controller supports seven external and 19 internal edge-triggered; (9)or level-sensitive interrupts ; (10)Programmable timers; (11)Software accessible event counters; (12)Two serial ports (16750 compatible UART); (13)One IIC interface; (14)General purpose I/O (GPIO) available; (15)Supports JTAG for board level testing; (16)Internal processor local bus (PLB) runs at SDRAM interface frequency; (17)Supports PowerPC processor boot from PCI memory.

Diagrams

|

PPC405CR |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PPC405EP |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PPC405EP-3GB266C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PPC440EP |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PPC440GP |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PPC440GR |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))